- Dec 15, 2021

- 2,356

- 1,275

- 106

Some are speculating this is an event to announce the Snapdragon X Plus

Some are speculating this is an event to announce the Snapdragon X Plus

Aye. And would match with SemiAccurate free snippet that QCOM wants to do an event for each new Snap X part that they announce.Some are speculating this is an event to announce the Snapdragon X Plus

From Mr. Swords yes?I was reading some past Snapdragon rumors and just learned on a reddit post from @FlameTail that

www.notebookcheck.net

www.notebookcheck.net

Not as insane as this:Phoenix M uses 1.1W. That's insanely low.

I WANT TO KNOW WHAT'A INSIDE THAT ARTICLE. I ma pretty sure it contains some information in additional to X Plus stuff.Aye. And would match with SemiAccurate free snippet that QCOM wants to do an event for each new Snap X part that they announce.

Yes, that's where the majority of the volume is for laptop sales.If QCOM is able to slot Snap X Plus on <$1000 machines and have good availability, it will be a game changer on mainstream laptops.

From your mouth into gods ears.Some are speculating this is an event to announce the Snapdragon X Plus

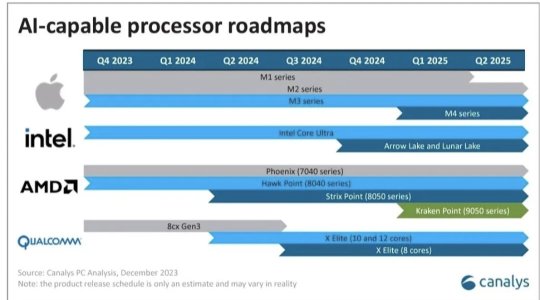

This is a slide from last October

View attachment 97278

And this is a much more recent slide:

View attachment 97279

Both are Geekbench 6 Multi-core, but in the new slide, the Snapdragon X Elite is consuming 10W less.

Is Qualcomm hiding something?

To me it looks like the first point on the horizontal axis is the same: slightly above 30W. But it might be due to me looking at the pictures on the phone.The comparison points also changed.

If that is indeed the case, that would be really impressive.Or they've improved their DVFS curve as development continued.

Works fine in lower case too, ya now ?I WANT TO KNOW WHAT'A INSIDE THAT ARTICLE. I ma pretty sure it contains some information in additional to X Plus stuff.

www.semiaccurate.com

www.semiaccurate.com

Want to know about Qualcomm’s upcoming Purwa SoC? SemiAccurate does too so here are some of the details that we know about.

This is far from a complete breakdown of the Purwa SoC we told you about earlier, more a random smattering of bullet points with a bit of speculation thrown in. Purwa is going to be called X Plus or something really close to that to differentiate it from the X Elite that is Homoa, and they are different dies. Both are also different from this too, and the other two we know about. In any case on with the show, and we don’t mean the dolphin (logo) show.

My speculation:

What is Qualcomm’s Purwa/X Pro SoC?

Want to know about Qualcomm’s upcoming Purwa SoC?www.semiaccurate.com

@FlameTail Another one 😛

The paywall is getting to me...@FlameTail Another one 😛

Very good, but there is no need for this if someone wirh a subscription can tell us the details.My speculation:

I'd rather halve either the memory bus or SLC, not both. I have a suspicion that even the big Snapdragon X Elite SoC is having only a measly 6 MB SLC.Snap X Plus => Targeting mainstream <$1000/$800 laptops

- 6 - 8C Phoenix Cores | 2P "Turbo Boost" cores + 6P Lower Clocked and reduced L2 cache. Or 2/4P Phoenix Cores + backported 4E Phoenix M cores

- 768/1024 ALU GPU. Based on Adreno 732 or Adreno 730 GFX IP

- NPU 45 TOPs

- Halved SLC and memory bus (64-bit LPDDR5X 8533)

- Targeting 10 - 15W for fanless or fanned laptops.

Target goals: Undercut AMD Kraken Point and Intel Lunar Lake while offering Apple M series of perf/W for mainstream consumers and beating LNL/KRK TTM by 2/3Q.

X Elite has a 6MB SLC? That's ridiculously low.I'd rather halve either the memory bus or SLC, not both. I have a suspicion that even the big Snapdragon X Elite SoC is having only a measly 6 MB SLC.

Agreed.We can guess only one of them is a cut of the same die as X Elite, and only one of them will be called X Plus.

Fwiw the M stuff is still only 8MB and so is LNL.X Elite has a 6MB SLC? That's ridiculously low.

It won’t be halved. I doubt that. Even the 7 series now has a 64-bit bus in phones. So no.And, right. If the Snap X Plus do halve the memory bus, they need to keep the SLC intact. But my speculation is based on the fact QCOM loves to save costs even at expense of performance on mobile SoCs.

Agreed.

No memory bus halved, they can’t get away with that and won’t anyway for the reasons I explained, it doesn’t make sense and even 7 series phone SoCs have it now. Will bet the farm against that for a part like this from Qualcomm.My speculation:

Snap X Plus => Targeting mainstream <$1000/$800 laptops

- 6 - 8C Phoenix Cores | 2P "Turbo Boost" cores + 6P Lower Clocked and reduced L2 cache. Or 2/4P Phoenix Cores + backported 4E Phoenix M cores

- 768/1024 ALU GPU. Based on Adreno 732 or Adreno 730 GFX IP

- NPU 45 TOPs

- Halved SLC and memory bus (64-bit LPDDR5X 8533)

- Targeting 10 - 15W for fanless or fanned laptops.

Target goals: Undercut AMD Kraken Point and Intel Lunar Lake while offering Apple M series of perf/W for mainstream consumers and beating LNL/KRK TTM by 2/3Q.

From Mr. Swords yes?

Qualcomm Snapdragon 8 Gen 4 power draw revealed by new rumour

A new rumour highlights the Snapdragon 8 Gen 4's power draw. When an all-core load is applied, the SoC's power consumption supposedly shoots up to 14.2 Watts, putting it well over the Snapdragon 8 Gen 3's 12.7 Watt figure.www.notebookcheck.net

Not as insane as this:

View attachment 97261

The most efficient E-core in the world.

If Purwa has only half the iGPU of the X Elite, it will be too weak (vs competition).Snap X Plus => Targeting mainstream <$1000/$800 laptops

- 6 - 8C Phoenix Cores | 2P "Turbo Boost" cores + 6P Lower Clocked and reduced L2 cache. Or 2/4P Phoenix Cores + backported 4E Phoenix M cores

- 768/1024 ALU GPU. Based on Adreno 732 or Adreno 730 GFX IP

- NPU 45 TOPs

- Halved SLC and memory bus (64-bit LPDDR5X 8533)

- Targeting 10 - 15W for fanless or fanned laptops.

Target goals: Undercut AMD Kraken Point and Intel Lunar Lake while offering Apple M series of perf/W for mainstream consumers and beating LNL/KRK TTM by 2/3Q.

I dont like this. I want it to have the same fmax as X Elite. That's one good thing about Apple Silicon- whether it's the base M chipvor the top tier M Ultra, the P-core runs at the same clock speed**But I think a 4+4 style die with reduced clocks on both (as in, targeting lower clocks, not segmenting after the fact, so if they target 3.6GHz max it changes the physical design)

That and the 4P+4E, i think they could get away with halving the memory bus.and a smaller Adreno could save probably like 20-40mm of area

If it's a 4P+4E CPU, I see no reason to cut down the L2 in half. In X Elite, a 4P cluster has 12 MB L2. Keep it as it is. For the 4E cluster, it might be 4 or 6 MB of L2.Cutting down L2 too much wouldn’t be wise though, it will hurt efficiency profiles and a bit of IPC. I think they should keep it as it is mostly.

LNL has an SLC?Fwiw the M stuff is still only 8MB and so is LNL.

512 KB L1 per core is monstrous. I doubt that, becuase if the cores indeed had 512 KB L1, I would think the IPC would be higher.It’d entirely possible it’s the L1 and they have 512KB of it, for 6MB total across 12 cores. The leaks had them having some L3 and SLC both fwiw, and I promise you the L1 is bigger than Arm’s cortex or Intel/AMD stuff currently, because of how big that shared L2 is.

Lolololol.LNL has an SLC?

512 KB L1 per core is monstrous. I doubt that, becuase if the cores indeed had 512 KB L1, I would think the IPC would be higher.

Apple at one point did have an L3 for what it’s worth and it’s not a big deal if they do or don’t. The Apple hallmark is really about big L1, wide but dense core and shared L2 clusters.Also the possibility that the 6 MB is an L3 is bizarre, considering that Oryon CPU is a design that traces it's heritage to Apple's CPUs, which do not have an L3.

They’re not, the SLC is accessible by the CPU now I believe.But maybe this makes sense for Qualcomm, if the CPU can't access the SLC. According to Andrei's findings (Anandtech article), in the Snapdragon 888, the CPU could not access the SLC, so the L3 functioned as effectively the LLC for the CPU. I don't know if Qualcomm is still doing this with recent chips like 8 Gen 2 or 8 Gen 3.